как реализуются параметры inout?

Я знаю, что такое параметры inout и как их использовать. Предположим, что у нас есть параметр inout io и мы хотим создать двунаправленную статическую оперативную память, такую как следующий код:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY sram IS

port(

clk : IN std_logic;

wr : IN std_logic;

io : INOUT std_logic;

addr : IN INTEGER RANGE 0 TO 7

);

END sram;

ARCHITECTURE behavioral OF sram IS

TYPE matrix IS ARRAY (0 TO 7) OF std_logic;

SIGNAL mem : matrix;

BEGIN

PROCESS(clk)

BEGIN

IF rising_edge(clk) THEN

IF wr = '1' THEN

mem(addr) <= io;

END IF;

END IF;

END PROCESS;

io <= mem(addr) WHEN wr = '0' ELSE 'Z';

END behavioral;

Мы можем создать экземпляр sram и записать на нем следующий код:

io <= '1' WHEN wr = '1' ELSE 'Z';

Вопрос: как инструмент синтеза может управлять несколькими назначениями и судить между несколькими драйверами ? Какое аппаратное обеспечение реализовано для этого ?

Спасибо за комментарии и ответы ...

2 ответа:

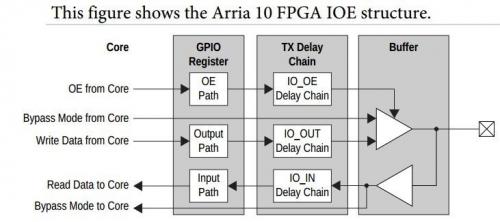

Для типичных ПЛИС и ASIC устройств реализация возможностей tristate доступна только на IO, как, например, в ПЛИС Altera Arria 10:

Таким образом, для таких устройств внутренние Ram всегда реализуются с выделенными входными и выходными портами, таким образом, не используя никаких внутренних возможностей tristate.

Даже если ОЗУ подключено к внешним IOs, которые поддерживают tristate, то внутренний блок ОЗУ все равно обычно создается с выделенным входом и выходные порты, поэтому соединение с выводом tristate на устройстве обрабатывается через буфер in-out с возможностью включения вывода и tristate.

Если внутренний дизайн пытается использовать возможности tristate или несколько драйверов, когда это не поддерживается устройством, то инструмент синтеза будет генерировать и ошибку, обычно говоря, что несколько драйверов не поддерживаются для одной и той же сети.

На устройствах Xilinx схема аналогична.

Это образ примитивного ИОБУФА:

Зеленая часть-это выходной драйвер с управлением tristate; синяя часть-входной драйвер. Полный IOB (блок ввода/вывода) состоит из нескольких примитивов:

- регистры IOB (input, output, tristate control)

- цепи задержки

- провода для объединения двух IOB в дифференциальный IOB (**BUFDS)

- возможность управлять тактовыми сетями (CC-IOB - часы способны IOB)

- pullup, pulldown, ...

- драйвер (IOBUF)

- pin / ball (IPAD, OPAD, IOPAD) - это включает защиту от ESD

Как работает синтез?

- Xilinx synthesis tools (XST / Synth) добавляет примитивы IPAD или OPAD для каждого провода в описании порта компонента верхнего уровня. Pad - это всего лишь примитив для представления физического штыря или шарика под пакетом FPGA.

- Если вы включили автоматическое добавление буферов ввода-вывода, инструмент добавит IBUF, OBUF, IOBUF, IBUFDS, ... примитивы между каждой панелью и портом верхнего уровня. Он использует направление порта (in, out, inout), чтобы определить правильный тип буфера. Если этот параметр отключен (по умолчанию = ВКЛ.), вам придется вручную добавлять буферы для каждого пин-кода ввода-вывода. В некоторых случаях XST обижается: я добавил несколько IOBUFs с контролем tristate вручную, поэтому XST отказался выводить недостающие буферы. Поэтому мне пришлось добавитьвсе буферы вручную ...

При использовании Xilinx XST это можно использовать шины tristate (направление порта = inout) ниже верхнего уровня. XST сообщит, что он добавил (виртуальные) буферы tristate. Эти буферы обрезаются, если направление каждого бита шины имеет очевидное направление и нет проблемы с несколькими драйверами.

Это не работает в iSim.